ISSN: 1682-3915

© Medwell Journals, 2016

## NoC Architecture: A Closer Look

Muhammad Athar Javed Sethi, Fawnizu Azmadi Hussin and Nor Hisham Hamid Department of Electrical and Electronic Engineering, Universiti Teknologi PETRONAS, 32610 Bandar Seri Iskandar, Perak, Malaysia

**Abstract:** Network on Chip (NoC) is a communication framework for on-chip network. NoC has implemented the concept of packet switching from data communication in on-chip network. NoC consists of multiple nodes Processing Elements (PEs) connected together through routers. Routers are in turns connected together through bidirectional interconnects. NI connects the PEs to routers as it separates the data communication of PE from network communication.

**Key words:** Network on Chip (NoC), clocking mechanism, evaluation parameters, open source, implementation, NoC size

## INTRODUCTION

NoC is a new solution for interconnection of Processing Elements (Pes) in System on Chip (SoC). NoC brings notable improvements over conventional bus. It has solved the delayed communication, congestion and higher latency problems. In this study, we are reviewing NoC architectures based on the different parameters which are: NoC clocking mechanism, evaluation parameters, topology, open source, implementation, NoC size, area, power dissipation/energy consumption, buffering and NoC routing algorithms.

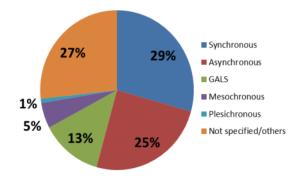

NoC clocking mechanism: Communication between router, NI and PE is mostly asynchronous, synchronous, Globally Asynchronous and Locally Synchronous (GALS), mesochronous, plesichronous heterochronous. According to literature search of the NoC architectures 29, 25, 13 and 5% of NoC architecture synchronous, asynchronous, mesochronous clocking mechanism as shown in Fig. 1. While only a single architecture uses plesichronous clocking mechanism. These trends show that the NoC architectures are moving from synchronous communication to asynchronous communication. The reason is that asynchronous communication is faster and data/activity dependent, exploiting average case rather than worst case performance (Amde et al., 2005; Itzhak et al., 2012; Emerson, 1997). Designing

Fig. 1: Clocking mechanism

Asynchronous NoC is modular but it is more complex compared to synchronous NoC (Emerson, 1997). Designing a glitch free circuit which at the same time manages multiple clocks is more difficult to manage than global clock based communication. Therefore, scientists and researchers combined the idea of synchronous and asynchronous NoC communication by having GALS architecture. GALS architecture solves the timing issues in multiple PEs in a NoC because local synchronous PEs need not to synchronize with a single global clock. GALS approach consumes less power as compared to global clock approach as local PEs have more control over their clock independent from other synchronous PEs (Agarwal et al., 2009a). It depends on the applications requirements mapped on the NoC that whether synchronous, asynchronous or GALS architecture will support it and will increase the performance of the NoC. The clock frequency of the NoC architectures is measure in Hertz (Hz). The scale of the frequency used by the NoC architectures is Mega (M) and Giga (G) hertz.

**Synchronous NoC:** In synchronous NoC all network is connected with a single clock. The activities are synchronized based on this clock. The benefit of synchronous communication are that all the changes at the routers, PE and links occur at the same time at regular clock period. Synchronous circuits have the problem of clock skew, lack of modularity, electromagnetic interference noise, worst case performance and clock power consumption issues (Amde *et al.*, 2005).

Examples of synchronous NoC are Dally et al (Dally and Towles, 2001), SPIN (Guerrier and Greiner, 2000), aSOC (Liang et al., 2000), ethereal (Rijpkema et al., 2003), OCN (Henriksson et al., 2003), Nostrum (Penolazzi and Jantsch, 2006; Millberg et al., 2004), Xpipes (Bertozzi and Benini, 2004), A 0.13 µm NoC (Mondinelli et al., 2004), RaSoC (Zeferino et al., 2004), QNoC (Bolotin et al., 2004), reconfigurable network on chip (Ching et al., 2005), a routing switch for on chip interconnection networks (Chi and Chen, 2004), spatial division multiplexing NoC (Leroy et al., 2005), CDMA router for on-chip switched networks (Kim et al., 2005), high throughput NoC architecture (Bouhraoua and Elrabaa, 2006), PnoC (Hilton and Nelson, 2006), CTNOC (Wang et al., 2006), low latency on chip network on chip multimedia applications (Lee et al., 2006a), NocMaker (Rufas et al., 2006), TILEPro64 (Bell et al., 2008), UT TRIPS (Gratz et al., 2007), Ambric (Butts, 2007), Polaris (Soteriou et al., 2007), TTNoC (Paukovits and Kopetz, 2008), ReNoC (Stensgaard and Sparso, 2008), XhiNoC (Samman et al., 2009), network on chip in a three dimensional (Feero and Pande, 2009), BiNoC (Lan et al., 2011), PMCNOC (Wang et al., 2010), WiNoC (Ganguly et al., 2011), dAElite (Stefan et al., 2014), Aurora (Qouneh et al., 2012), RecMIN (Logvinenko et al., 2013), SWIFT (Postman et al., 2013) and TagNoC (Yaghini et al., 2015).

Asynchronous NoC: In asynchronous NoC activities are performed based on the handshake (control) signals shared between routers (Amde *et al.*, 2005; Bjerregaard and Mahadevan, 2006; Yaghini *et al.*, 2015). Asynchronous NoC are also called self-timed NoC (Bainbridge and Furber, 2002). Asynchronous circuit implementation usually takes more area, delay, power consumption and consumes channel bandwidth as compared to synchronous approach because of explicit sharing of signals (Amde *et al.*, 2005). It is not easy to resynchronize the asynchronous communication. The

resynchronization introduces error bits and increase the latency and power consumption (Bjerregaard and Mahadevan, 2006). The asynchronous communication is faster as compared to synchronous communication at high traffic loads as it has the least latency (Bjerregaard and Mahadevan, 2006; Itzhak et al., 2012). In asynchronous NoC there can be no timing relationship between synchronous clocks (Pes). Asynchronous provides the maximum flexibility in terms of timings (Teehan et al., 2007). When interconnects are idle, apart from the leakage, no power is consumed in asynchronous NoC. This solves the problem of increasing power consumption as the chip size is increased (Bjerregaard and Mahadevan, 2006).

CHAIN (Bainbridge and Furber, 2002), ethereal (Rijpkema et al., 2003), HERMES (Moraes et al., 2004), BIDI-MIN (Pande et al., 2003), SoCIN (Zeferino and Susin, 2003), R<sup>2</sup>NoC (Samuelsson and Kumar, 2004), Fspider (Evain et al., 2004), Spidergon (Coppola et al., 2004), asynchronous on chip network router with quality of service (Feliciian and Furber, 2004), Mango (Bjerregaard and Sparso, 2005a, b; Wolkotte et al., 2005), ASPIDA (Amde et al., 2005), topology adaptive NoC (Bartic et al., 2005), asynchronous NoC architecture (Beigne et al., 2005), cross road interconnection architecture (Chang et al., 2006), SCC (Hoffman et al., 2007), a reconfigurable baseband platform based asynchronous NoC (Paukovits and Kopetz, 2008), EVC (Kumar et al., 2008), HT-OCTAGON DRNoC (Krasteva et al., 2010), dynamic reconfigurable network on chip (Wu et al., 2011), Ramos (Pena and Michel, 2011), BMNoC (Lee et al., 2012), Custom Network on Chip architecture (Mishra et al., 2012), DANoC (Shu et al., 2012), AdNoC (Al Faruque et al., 2012) and mesh based NoC (Choudhary and Qureshi, 2012) are asynchronous NoCs.

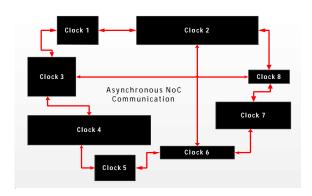

Globally Asynchronous Locally Synchronous (GALS): In the Globally Asynchronous Locally Synchronous (GALS) approach the NoC is divided among multiple sub systems. Each sub-system has its own clock and they communicate with other system through asynchronous NoC communication. GALS have less power consumption as compared to having a global clock. It avoids the problem of clock synchronization due to clock skew as more and more devices are coming on the chip (Amde *et al.*, 2005; Teehan *et al.*, 2007; Tortosa *et al.*, 2004). Figure 2 shows the GALS architecture where independent synchronous islands of systems are connected with asynchronous NoC through irregular topology.

CLICHE (Kumar et al., 2002), PROTEO, Nexus (Lines, 2004), an architecture and compiler for aSoC

Fig. 2: GALS clocking scheme

(Liang et al., 2004), on-chip network for low power heterogeneous SoC platform (Kangmin et al., 2004), Arteris, ProtoNoC (Rufas et al., 2006), TTNoC (Schoeberl, 2007), MoCRes (Janarthanan et al., 2007), CDMA NoC (Wang et al., 2007), MoCSYS (Janarthanan and Tomko, 2008), Aelite (Hansson et al., 2009), ALPIN (Beigne et al., 2009), RAMPSoC (Gohringer et al., 2010) and WaveSync (Yang et al., 2014) are following GALS approach.

**Mesochronous:** Due to clock skew concept a new clocking scheme called mesochronous is used. In this scheme all the subsystems have different clocks with the same frequency but the phase is different (Wiklund and Liu, 2003). Ethereal (Rijpkema *et al.*, 2003), SoCBUS (Wiklund and Liu, 2003), adaptive network on chip (Lee *et al.*, 2006), low-power network on chip (Lee *et al.*, 2006b) and Intel TeraFLOPS (Vangal *et al.*, 2008) are examples of mesochronous links.

**Plesichronous NoC:** In plesichronous NoC, the source and destination PE operate at the nominal frequency which may be slightly different and this leads to drifting phase (Teehan *et al.*, 2007). The Star Connected OCN (Lee *et al.*, 2003) is a plesichronous NoC.

**Heterochronous NoC:** In a heterochronous NoC, source and destination have totally different clock frequencies (Teehan *et al.*, 2007).

**Evaluation parameters:** The NoC architectures are evaluated based on various parameters. These parameters include latency, throughput, bandwidth utilization, area, power dissipation, energy consumption, etc. Every NoC architecture tries to maximize the throughput and bandwidth utilization while minimize latency, area, power

and energy dissipation using varrious techniques. Latency refers to the time taken by a packet or flitlatency is measured in nano seconds (ns). Throughput is the number of bits that can be sent across the NoC interconnect (link) per second. Throughput is measured in bits per second (bps). Bandwidth is the maximum number of bits that can be sent over a interconnect (link) per second. The unit of bandwidth is bits per second (bps). Area refers to the size of NoC after synthesis. Now a days there are also some software tools available which can be used to measure the area and power consumption of the NoC architecture. The unit of area used by most of the architecture is mm<sup>2</sup>. The units of power and energy consumption used by the architectures are milli-Watt (mW) and petajoule (pJ), respectively. When packets traverses the router and interconnects it consumes power and energy. These parameters are very important to calculate as more and more heterogeneous devises (PEs) are coming onto chips. They increase the power, energy and area consumption of the chip.

**Topology:** The topology of the NoC defines how the PEs, routers and links are connected with each other in the network. The selection of the particular topology for any specific NoC depends on the communication usage of the PE's. Other factors in choosing a specific topology for any NoC design include its impact on performance and cost parameters. The performance parameters include latency, fault tolerance, bandwidth and throughput while cost parameters include area and power/energy consumption (Ogras et al., 2005). Many different topologies have been proposed (Wang et al., 2011). There are broadly two categories of topologies, regular and irregular topologies. In regular topologies routers and PEs are connected according to some pattern, e.g., mesh, torus, fat tree, butterfly fat tree, octagon, star, hierarchical star, crossbar, ring, spidergon, chain, subnets, generalized de bruijin topology. While, there is no common pattern in irregular topology which may include hybridize topologies. Although, regular NoC topologies are simple to implement, at times they have the drawback being non-optimal in terms of network utilization. The low network utilization leads to delayed communication and increased power consumption. In order to overcome these drawbacks scientists come up with the concept of irregular topologies. Irregular or custom NoC topologies are application specific and mostly have heterogeneous PE's, routers as compared to regular NoC topologies (Tatas et al., 2014). Regular topologies make the routing decision simple and it is easily replicated on multiple

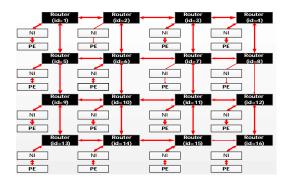

Fig. 3: Mesh topology

nodes while irregular topologies make the routing algorithm more complex (Guerrier and Greiner, 2000).

In the mesh topology, the routers are connected with each other through point to point connection in a mesh structure as shown in Fig. 3. The routers at the first and last column or row of NoC are not connected with any other neighbour routers. Most of the NoC architectures have mesh topology because its communication structure is less complex and it is also similar to 2D silicon surface (Teehan *et al.*, 2007; Seifi and Eshghi, 2012). One of the drawbacks of the mesh topology is congestion at the center of the NoC due to the routing algorithm. In mesh topology, routing algorithm should have equal and balance traffic distribution mechanism.

The torus topology is similar to mesh except that the first and last column or row elements are also connected with each other. Torus increases and eases the routing decisions Torus topology solves the excessive round end trip delays as they are connected together. The drawback of the torus topology is more area and links requirement than mesh NoC (Wang et al., 2011). In tree structure topologies the routers are connected in a hierarchical design such that the parent's routers have child routers connected with them. The tree topology is hierarchical in structure but becomes complex as more PE's are connected at the leaf routers (Guerrier and Greiner, 2000). In the tree base topology the traffic can be easily disseminated to the desire destination due to hierarchical structure (Bjerregaard and Mahadevan, 2006). In star topology, the routers are connected with the centralized arbiter. The arbiter manages the communication between multiple routers. The arbiter may be a specialized device or it can be a router as well (Lee et al., 2003). The capacity of the centralized arbiter/router should be large to manage the traffic received from multiple PE's connected to it. This at times also leads to congestion at the centralized switch.

In the octagon topology, the eight routers are connected in a ring fashion with bidirectional wires (Karim et al., 2002). Octagon topology is simple to implement. Fast and efficient routing algorithm can be implemented using this topology. Excessive wiring is required in order to extend the octagon network to more than eight Pes. In crossbar topology the router are connected with a number of wires connected in a crossbar fashion. This topology is simple to implement but the links between PEs become complex and large as more and more PE's are connected through crossbar interconnection (Lines, 2004). Ring topology refers to the nodes connected in a ring (Samuelsson and Kumar, 2004). That is all routers are connected with each other through interconnects in a ring shape. Although, ring topology is simple to implement but it have limited scalability and performance problem as the number of nodes are increased. In the spidergon topology, number of nodes (>2) is connected together in a bidirectional ring in both clockwise and anti-clock wise direction. So, the nodes in spidergon is also connected with the cross connection. Spidergon topology is similar to spider web. This topology is regular, scalable, point-to-point and has good network diameter. The network becomes complex as the number of PEs are increased (Coppola et al., 2004). In the subnet topology, there are small groups of PEs connected with the router. This group is called subnet. These subnets are in return connected with each other. The PEs which communicates oftenly are put in the same subnet. This makes the communication between PEs more efficient. The communication between PE in different subnets takes more time for communication which may leads to delayed communication (Hilton and Nelson, 2006). In de bruijin topology the nodes are connected through vertices and it can be an irregular topology (Soteriou et al., 2007). It is an efficient topology for parallel processing and is also suitable for VLSI implementation. The two dimensional de bruijin NoC is performing better as compared to two dimensional mesh topology in terms of latency and energy dissipation. At times, in two dimensional de bruijin NoC it takes longer links to connect the neighbour node as compared to two dimensional meshes, this increases the network area.

**Open source:** The open source software/architecture has a license which allows the end user to have access to the source code, redistribute the software/architecture and modify the original code with the same license. At times, the license may have special provision to be met specifically. For example, the derived

software/architecture should use its own name and version apart from mentioning software/architecture name. Open source architectures and codes are usually provided for academic and research purposes. They are mostly not allowed to be used for commercial purpose. Ethereal (Rijpkema et al., 2003), Aelite (Hansson et al., 2009) and dAElite (Stefan et al., 2014) architectures are not open source while Nostrum (Penolazzi and Jantsch, 2006; Millberg et al., 2004) is provided on request. Reconfigurable Network on Chip (Ching et al., 2005) and NocMaker (Rufas et al., 2006) are open source architectures. Other NoC architectures have not mentioned any information regarding it.

Implementation: The NoC architectures are implemented on simulator, Field Programmable Gate Array (FPGA) (Shanthi, 2014) and as Application Specific Integrated Circuits (ASIC). Some of the architectures are synthesized using a cycle accurate simulator. The simulators used are HNOCS (Itzhak *et al.*, 2012), OMNET++(Varga and Hornig, 2008), NS-2, OPNET (Modeler, 2009), Noxim (Palesi *et al.*, 2010), Nirgam, Simics (River, 2006), Garnet (Agarwal *et al.*, 2009b), Orion (Wang *et al.*, 2007, 2010, 2011), Spice (Franco *et al.*, 2015), Recsim (Logvinenko and Tutsch, 2012) and CACTI (Muralimanohar *et al.*, 2007).

**NoC size:** NoC architectures have used various NoC sizes for implementation purpose. These sizes include  $2\times2$ ,  $3\times3$ ,  $4\times4$ ,  $5\times5$ ,  $6\times6$ ,  $7\times7$ ,  $8\times8$ ,  $5\times8$ ,  $2\times3$ ,  $4\times3$  having two dimensional mesh and torus topologies. Some of the NoC topologies were regular while others were irregular.

**Area:** Some of the papers mentioned the area of the complete NoC architecture while few specified the router or switch area. The area is usually measured as the total number of look up tables or slices used in FPGA or the number of gates/transistors/flip flops/logic cells used in the NoC architecture. The area of the router and NoC architectures are also mentioned in mm², µm² units. In embedded systems, area and power consumption of the devices are very much important.

Power dissipation/energy consumption: This is a very important parameter of NoC architectures. Scientists and researchers are finding techniques to efficiently utilize the power and energy consumption of the NoC. The NoC clocking mechanism, buffer management, routing algorithms and switching activities consumes power and energy on a per router and interconnect basis. The units used for power dissipation are  $\mu W$  (micro-Watt), mW

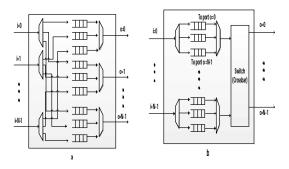

Fig. 4: Output queue and VOQ router architecture

(milli-Watt) and MW (Mega-Watt) while the units used for energy consumption is pj (peta-joule) and pj/packet (peta-joule per packet).

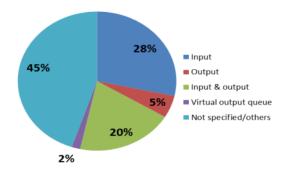

**Buffering:** Buffer is the integral part of any network router (Bjerregaard and Mahadevan, 2006) but they consume a lot of power in NoC. Therefore, efficient buffer design is very important for optimized NoC performance. The buffer design includes the location and size of the buffer (Bjerregaard and Mahadevan, 2006). To minimize the access latency and implementation cost, it is always preferred to use registers rather than huge memories in the form of SRAM or DRAM (Hu and Marculescu, 2003). The location of the buffers can be at the input or output port of the router. These buffers are called as the input queue and output queue. The performance of the output buffering is the best as compared to other strategies but at the cost of more loads on interconnects. When to read the flits from input or output queue depends on the scheduler which in turns checks the output port that whether it is free. Usually router used to have one queue per port but due the HOL problem now they have more than one queue per port for every connection. The Virtual Output Queue (VOQ) is one type of input buffering which has the combined benefits of input and output queuing (Rijpkema et al., 2003). The input queues may have less memory cost as they have fewer queues as compared to VOO and output buffers techniques (Radulescu and Goossens, 2004). Input queues also solve the problem of HOL as the output queues may be blocked due to congestion or faulty interconnects (Bjerregaard and Mahadevan, 2006). Figure 4 shows the output and virtual output queue architectures of routers.

According to the literature search, 28% of NoC architectures are using input queues while 20% of architectures are using input and output queues together. 5% of architectures are using only output queues while only two architectures are using VOQ's as shown in

Fig. 5: Buffering

Fig. 5. This shows the trend that most of the scientists preferred input and combination of input and output buffers because of better link utilization and performance.

The area of the NoC increases directly as the size of the input buffers is increased. Ogras *et al.* (2005), it is mentioned that the 4×4 NoC area increases by 30% as the input buffer size are increased from 2-3 words. But at certain times, depending on the network load the network latency is reduced a considerable amount by increasing the buffer size. However, due to heterogeneous traffic generated by PEs in NoC, it is always desirable to allocate more buffers for high traffic channels while small number of buffers can be allocated to low traffic channels.

OCTAGON (Karim et al., 2002), CLICHE (Kumar et al., 2002), ethereal (Rijpkema et al., 2003), HERMES (Moraes et al., 2004), SoCIN (Zeferino and Susin, 2003), µSpider (Evain et al., 2004), RaSoC (Zeferino et al., 2004), QNoC (Bolotin et al., 2004), reconfigurable network on chip (Ching et al., 2005), DyAD (Hu and Marculescu, 2004), a routing switch for on chip interconnection networks (Chi and Chen, 2004), asynchronous on chip network router with quality of service (Feliciian and Furber, 2004; Kavaldjiev et al., 2006), INoC (Neeb and Wehn, 2008), CTNOC (Wang et al., 2006), low latency on chip network (Mullins et al., 2006), low-power network on chip (Lee et al., 2006b), intel teraFLOPS (Vangal et al., 2008), EVC (Kumar et al., 2008), ReNoC (Stensgaard and Sparso, 2008), Aelite (Hansson et al., 2009), XhiNoC (Samman et al., 2009), BiNoC (Lan et al., 2011), DRNoC (Krasteva et al., 2010), PMCNOC (Wang et al., 2010), dynamic reconfigurable network on chip (Wu et al., 2011), Kilo-NoC (Grot et al., 2011), BMNoC (Lee et al., 2012), DANoC (Shu et al., 2012), WaveSync (Yang et al., 2014), RecMIN (Logvinenko et al., 2013), SWIFT (Postman et al., 2013) and BLOCON (Kao and Chao, 2014) have the input queues at the router port.

These are the NoC architectures having output queues at the router port; RAW (Taylor et al., 2002),

Eclipse (Forsell, 2002), Xpipes (Bertozzi and Benini, 2004), Mango (Bjerregaard and Sparso, 2005, 2004a, b), topology adaptive NoC (Bartic *et al.*, 2005) and on chip multimedia applications (Lee *et al.*, 2006a).

The NoC architectures which are supporting input and output queues are; SPIN (Guerrier and Greiner, 2000), aSOC (Liang et al., 2000), Dally et al (Dally and Towles, 2001), micronetwork (Wingard, 2001), PROTEO, BIDI-MIN (Pande et al., 2003), Nostrum (Penolazzi and Jantsch, 2006; Millberg et al., 2004), A 0.13 µm NoC (Mondinelli et al., 2004), NoCGen (Chan and Parameswaran, 2004), CDMA router for on-chip switched networks (Kim et al., 2005), DSPIN (Panades et al., 2006), XGFT (Kariniemi and Nurmi, 2006), PnoC (Hilton and Nelson, 2006), HIBI (Salminen et al., 2006), TILEPro64 (Bell et al., 2008), UT TRIPS (Gratz et al., 2007), Ambric (Butts, 2007), Generalized de Bruijn Graph NoC (Hosseinabady et al., 2007), HT-OCTAGON, ALPIN (Beigne et al., 2009), dAElite (Stefan et al., 2014), AdNoC (Faruque et al., 2012) and HELIX (Bahirat and Pasricha, 2014). ArtNoC (Schuck et al., 2007) and BLOCON (Kao and Chao, 2014) NoC architectures have VOQ.

**NoC routing algorithms:** There are five broad categories of routing algorithms which are deterministic, stochastic, fully adaptive, partial adaptive and bio-inspired routing algorithms. Detail about these routing algorithms can be found in Sethi *et al.* (2013a, b, 2014, 2016a, b)

## CONCLUSSION

In this study, we are looking and reviewing NoC architectures based on different aspects.

## REFERENCES

Agarwal, A., C. Iskander and R. Shankar, 2009a. Survey of Network on Chip (NOC) architectures and contributions. J. Eng. Comput. Archit., 3: 21-27.

Agarwal, N., T. Krishna, L.S. Peh and N.K. Jha, 2009b. GARNET: A detailed on-chip network model inside a full-system simulator. Proceedings of the IEEE International Symposium on Performance Analysis of Systems and Software, April 26-28, 2009, IEEE, New York, USA., ISBN: 978-1-4244-4184-6, pp. 33-42.

Al Faruque, M.A., T. Ebi and J. Henkel, 2012. AdNoC: Runtime adaptive network-on-chip architecture. IEEE Trans. Very Large Scale Integr. Syst., 20: 257-269.

Amde, M., T. Felicijan, A. Efthymiou, D. Edwards and L. Lavagno, 2005. Asynchronous on-chip networks. IEEE. Proc. Comput. Digital Tech., 152: 273-283.

- Bahirat, S. and S. Pasricha, 2014. HELIX: Design and synthesis of hybrid nanophotonic application-specific network-on-chip architectures. Proceedings of the 15th International Symposium on Quality Electronic Design, March 3-5, 2014, IEEE, New York, USA., ISBN: 978-1-4799-3946-6, pp: 91-98.

- Bainbridge, J. and S. Furber, 2002. Chain: A delay-insensitive chip area interconnect. IEEE. Micro, 22: 16-23.

- Bartic, T.A., J.Y. Mignolet, V. Nollet, T. Marescaux and D. Verkest *et al.*, 2005. Topology adaptive network-on-chip design and implementation. IEEE. Proc. Comput. Digital Tech., 152: 467-472.

- Beigne, E., F. Clermidy, H. Lhermet, S. Miermont and Y. Thonnart *et al.*, 2009. An asynchronous power aware and adaptive NoC based circuit. IEEE. J. Solid State Circuits, 44: 1167-1177.

- Beigne, E., F. Clermidy, P. Vivet, A. Clouard and M. Renaudin, 2005. An asynchronous NOC architecture providing low latency service and its multi-level design framework. Proceedings of the 11th IEEE International Symposium on Asynchronous Circuits and Systems, March 14-16, 2005, IEEE, New York, USA., ISBN: 0-7695-2305-6, pp: 54-63.

- Bell, S., B. Edwards, J. Amann, R. Conlin and K. Joyce et al., 2008. Tile 64-processor: A 64-core soc with mesh interconnect. Proceedings of the 2008 IEEE International Conference on Solid-State Circuits Digest of Technical Papers, Feburary 3-7, 2008, IEEE, NEW York, USA., ISBN: 978-1-4244-2010-0, pp: 88-598.

- Bertozzi, D. and L. Benini, 2004. Xpipes: A network-onchip architecture for gigascale systems-on-chip. IEEE. Circuits Syst. Mag., 4: 18-31.

- Bjerregaard, T. and J. Sparso, 2004. Virtual channel designs for guaranteeing bandwidth in asynchronous network-on-chip. Proceedings of the Conference on Norchip, Novembr 8-9, 2004, IEEE, New York, USA., ISBN: 0-7803-8510-1, pp: 269-272

- Bjerregaard, T. and J. Sparso, 2005a. Scheduling discipline for latency and bandwidth guarantees in asynchronous network-on-chip. Proceedings of the 11th IEEE International Symposium on Asynchronous Circuits and Systems, March 14-16, 2005, IEEE, New York, USA., ISBN: 0-7695-2305-6, pp: 34-43.

- Bjerregaard, T. and J. Sparso, 2005b. A router architecture for connection-oriented service guarantees in the MANGO clockless network-on-chip. Proceedings of the IEEE Conference on Design, Automation and Test in Europe, March 7-11, 2005, IEEE, New York, USA., ISBN: 0-7695-2288-2, pp: 1226-1231.

- Bjerregaard, T. and S. Mahadevan, 2006. A survey of research and practices of network-on-chip. ACM. Comput. Surv., Vol.38,

- Bolotin, E., I. Cidon, R. Ginosar and A. Kolodny, 2004.

QNoC: QoS architecture and design process for network on chip. J. Syst. Architecture, 50: 105-128.

- Bouhraoua, A. and M.E. Elrabaa, 2006. A high-throughput network-on-chip architecture for systems-on-chip interconnect. Proceedings of the 2006 International Symposium on System-on-Chip, November 13-16, 2006, IEEE, New York, USA., ISBN: 1-4244-0621-8, pp: 1-4.

- Butts, M., 2007. Synchronization through communication in a massively parallel processor array. IEEE. Micro, 27: 32-40.

- Chan, J. and S. Parameswaran, 2004. NoCGEN: A template based reuse methodology for networks on chip architecture. Proceedings of the 17th International Conference on VLSI Design, January 9-9, 2004, IEEE, New York, USA., ISBN: 0-7695-2072-3, pp: 717-720

- Chang, K.C., J.S. Shen and T.F. Chen, 2006. Evaluation and design trade-offs between circuit-switched and packet-switched NOCs for application-specific SOCs. Proceedings of the 43rd Annual Conference on Design Automation, July 24-28, 2006, ACM, New York, USA., ISBN:1-59593-381-6, pp: 143-148.

- Chi, H.C. and J.H. Chen, 2004. Design and implementation of a routing switch for on-chip interconnection networks. Proceedings of the 2004 IEEE Asia-Pacific Conference on Advanced System Integrated Circuits, August 5-5, 2004, IEEE, New York, USA., ISBN: 0-7803-8637-X, pp. 392-395.

- Ching, D., P. Schaumont and I. Verbauwhede, 2005. Integrated modelling and generation of a reconfigurable network-on-chip. Intl. J. Embedded Syst., 1: 218-227.

- Choudhary, S. and S. Qureshi, 2012. Performance evaluation of mesh-based NoCs: Implementation of a new architecture and routing algorithm. Intl. J. Autom. Comput., 9: 403-413.

- Coppola, M., R. Locatelli, G. Maruccia, L. Pieralisi and A. Scandurra, 2004. Spidergon: A novel on-chip communication network. Proceedings of the 2004 International Symposium on System-on-Chip, November 16-18, 2004, IEEE, New York, USA., ISBN: 0-7803-8558-6, pp: 15-15.

- Dally, W.J. and B. Towles, 2001. Route packets, not wires: On-chip interconnection networks. Proceedings of the Design Automation Conference, June 18-22, 2001, Las Vegas, Nev, USA., pp. 684-689.

- Emerson, K., 1997. Asynchronous design-An interesting alternative. Proceedings of the 10th International Conference on VLSI Design, January 4-7, 1997, New York, USA., ISBN: 0-8186-7755-4, pp: 318-320.

- Evain, S., J.P. Diguet and D. Houzet, 2004. i spider: A CAD tool for efficient NoC design. Proceedings of the Conference on Norchip, November 8-9, 2004, IEEE, New York, USA., ISBN: 0-7803-8510-1, pp: 218-221.

- Feero, B.S. and P.P. Pande, 2009. Networks-on-Chip in a Three-dimensional environment: A performance evaluation. IEEE Trans. Comput., 58: 32-45.

- Feliciian, F. and S.B. Furber, 2004. An asynchronous on-chip network router with Quality-of-Service (QoS) support. Proceedings of the IEEE International Conference on SOC, September 12-15, 2004, IEEE, New York, USA., ISBN: 0-7803-8445-8, pp. 274-277.

- Forsell, M., 2002. A scalable high-performance computing solution for networks on chips. IEEE. Micro, 22: 46-55.

- Franco, F.J., C. Palomar, J.G. Izquierdo and J.A. Agapito, 2015. SPICE simulations of single event transients in bipolar analog integrated circuits using public information and free open source tools. IEEE. Trans. Nucl. Sci., 62: 1625-1633.

- Ganguly, A., K. Chang, S. Deb, P.P. Pande and B. Belzer *et al.*, 2011. Scalable hybrid wireless network-on-chip architectures for multicore systems. IEEE. Trans. Comput., 60: 1485-1502.

- Gohringer, D., M. Hubner, L.H. Derville and J. Becker, 2010. Message passing interface support for the runtime adaptive multi-processor system-on-chip RAMPSoC. Proceedings of the 2010 International Conference on Embedded Computer Systems (SAMOS), July 19-22, 2010, IEEE, New York, USA., ISBN: 978-1-4244-7938-2, pp: 357-364.

- Gratz, P., C. Kim, K. Sankaralingam, H. Hanson and P. Shivakumar *et al.*, 2007. On-chip interconnection networks of the TRIPS chip. IEEE. Micro, 27: 41-50.

- Guerrier, P. and A. Greiner, 2000. A generic architecture for on-chip packet-switched interconnections. Proceedings of the conference on Design, automation and test in Europe, March 27-30, 2000, ACM, New York, USA., ISBN: 1-58113-244-1, pp: 250-256.

- Hilton, C. and B. Nelson, 2006. PnoC: A flexible circuit-switched NoC for FPGA-based systems. IEE. Proc. Comput. Digital Tech., 153: 181-188.

- Hosseinabady, M., M.R. Kakoee, J. Mathew and D.K. Pradhan, 2007. Reliable network-on-chip based on generalized de Bruijn graph. Proceedings of the IEEE International Workshop on High Level Design Validation and Test, November 7-9, 2007, IEEE, New York, USA., ISBN: 978-1-4244-1480-2, pp. 3-10.

- Hu, J. and R. Marculescu, 2003. Exploiting the routing flexibility for energy/performance aware mapping of regular NOC architectures. Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, March 3-7, 2003, Munich, Germany, pp: 688-693.

- Hu, J. and R. Marculescu, 2004. DyAD: Smart routing for networks-on-chip. Proceedings of the 41st Annual Conference on Design Automation, June 7-11, 2004, ACM, New York, USA., ISBN:1-58113-828-8, pp: 260-263.

- Itzhak, Y.B., E. Zahavi, I. Cidon and A. Kolodny, 2012. HNOCS: Modular open-source simulator for heterogeneous NoCs. Proceedings of the IEEE 2012 International Conference on Embedded Computer Systems (SAMOS), July 16-19, 2012, IEEE, New York, USA., ISBN: 978-1-4673-2297-3, pp: 51-57.

- Janarthanan, A. and K.A. Tomko, 2008. MoCSYS: A multi-clock hybrid two-layer router architecture and integrated topology synthesis framework for system-level design of FPGA based on-chip networks. Proceedings of the 21st International Conference on VLSI Design (VLSID 2008), January 4-8, 2008, IEEE, New York, USA., ISBN: 0-7695-3083-4, pp: 397-402.

- Janarthanan, A., V. Swaminathan and K.A. Tomko, 2007. MoCReS: An area-efficient multi-clock on-chip network for reconfigurable systems. Proceedings of the IEEE Annual Symposium on Computer Society VLSI, March 9-11, 2007, IEEE, New York, USA., ISBN: 0-7695-2896-1, pp: 455-456.

- Kao, Y.H. and H.J. Chao, 2014. Design of a bufferless photonic clos network-on-chip architecture. IEEE. Trans. Comput., 63: 764-776.

- Karim, F., A. Nguyen and S. Dey, 2002. An interconnect architecture for networking systems on chips. IEEE. Micro, 22: 36-45.

- Kariniemi, H. and J. Nurmi, 2006. On-line reconfigurable XGFT network-on-chip designed for improving the fault-tolerance and manufacturability of the MPSoC chips. Proceedings of the 2006 International Conference on Field Programmable Logic and Applications, August 28-30, 2006, IEEE, New York, USA., ISBN: 1-4244-0312-X, pp: 1-6.

- Kavaldjiev, N., G.J. Smit, P.G. Jansen and P.T. Wolkotte, 2006. A virtual channel network-on-chip for GT and BE traffic. Proceedings of the IEEE Annual Symposium on Computer Society Emerging VLSI Technologies and Architectures (ISVLSI'06), March 2-3, 2006, IEEE, New York, USA., ISBN: 0-7695-2533-4, PP: 6-6.

- Krasteva, Y.E., E.D.L. Torre and T. Riesgo, 2010. Reconfigurable networks on chip: DRNoC architecture. J. Syst. Archit., 56: 293-302.

- Kumar, A., L.S. Peh, P. Kundu and N.K. Jha, 2008. Toward ideal on-chip communication using express virtual channels. IEEE. Micro, 28: 80-90.

- Kumar, S., A. Jantsch, M. Millberg, J. Oberg and J.P. Soininen et al., 2002. A network on chip architecture and design methodology. Proceedings of the IEEE Computer Society Annual Symposium on VLSI, April 26-26, 2002, Pittsburgh, PA., USA., pp: 105-112.

- Lan, Y.C., H.A. Lin, S.H. Lo, Y.H. Hu and S.J. Chen, 2011.

A bidirectional NoC (BiNoC) architecture with dynamic self-reconfigurable channel. IEEE.

Trans. Comput. Aided Des. Integr. Circuits Syst., 30: 427-440.

- Lee, H.G., U.Y. Ogras, R. Marculescu and N. Chang, 2006a. Design space exploration and prototyping for on-chip multimedia applications. Proceedings of the 43rd Annual Conference on Design Automation, July 24-28, 2006, ACM, New York, USA., ISBN:1-59593-381-6, pp: 137-142.

- Lee, K., S.J. Lee and H.J. Yoo, 2006b. Low-power network-on-chip for high-performance SoC design. IEEE Trans. Very Large Scale Integr. Syst., 14: 148-160.

- Lee, S., N. Togawa, Y. Sekihara, T. Aoki and A. Onozawa, 2012. A hybrid NoC architecture utilizing packet transmission priority control method. Proceedings of the 2012 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), December 2-5, 2012, IEEE, New York, USA., ISBN: 978-1-4577-1729-1, pp: 404-407.

- Lee, S.J., K. Kim, H. Kim, N. Cho and H.J. Yoo, 2005. Adaptive network-on-chip with wave-front train serialization scheme. Proceedings of the Symposium on VLSI Circuits Digest of Technical Papers, June 16-18, 2005, USA., pp: 104-107.

- Lee, S.J., S.J. Song, K. Lee, J.H. Woo and S.E. Kim *et al.*, 2003. An 800MHz star-connected on-chip network for application to systems on a chip. Proceedings of the 2003 IEEE International Conference on Solid-State Circuits Digest of Technical Papers, February 13-13, 2003, IEEE, New York, USA., ISBN: 0-7803-7707-9, pp: 468-469.

- Leroy, A., P. Marchal, A. Shickova, F. Catthoor and F. Robert et al., 2005. Spatial division multiplexing: a novel approach for guaranteed throughput on NoCs. Proceedings of the 3rd IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis, September 19-21, 2005, ACM, New York, USA., ISBN:1-59593-161-9, pp: 81-86.

- Liang, J., A. Laffely, S. Srinivasan and R. Tessier, 2004. An architecture and compiler for scalable on-chip communication. IEEE. Trans. Very Large Scale Integr. Syst., 12: 711-726.

- Liang, J., S. Swaminathan and R. Tessier, 2000. ASOC: A scalable, single-chip communications architecture. Proceedings of the International Conference on Parallel Architectures and Compilation Techniques, October 15-19, 2000, Philadelphia, PA., pp. 37-46.

- Lines, A., 2004. Asynchronous interconnect for synchronous SoC design. IEEE. Micro, 24: 32-41.

- Logvinenko, A., C. Gremzow and D. Tutsch, 2013. RecMIN: A reconfiguration architecture for network on chip. Proceedings of the 2013 8th International Workshop on Reconfigurable and Communication-Centric Systems-on-Chip (ReCoSoC), July 10-12, 2013, IEEE, New York, USA., ISBN: 978-1-4673-6180-4, pp. 1-6.

- Millberg, M., E. Nilsson, R. Thid and A. Jantsch, 2004. Guaranteed bandwidth using looped containers in temporally disjoint networks within the Nostrum network on chip. Proceedings of the Conference on Design, Automation and Test in Europe and Exhibition, February 16-20, 2004, IEEE, New York, USA., ISBN: 0-7695-2085-5, pp. 890-895.

- Mishra, P., A. Nidhi and J.K. Kishore, 2012. Custom network on chip architecture for map generation in autonomous navigating robots. Proceedings of the 2012 IEEE Annual Conference on India (INDICON), December 7-9, 2012, IEEE, New York, USA., ISBN: 978-1-4673-2272-0, pp. 086-091.

- Moraes, F., N. Calazans, A. Mello, L. Moller and L. Ost, 2004. HERMES: An infrastructure for low area overhead packet-switching networks on chip. Integr. VLSI. J., 38: 69-93.

- Moursy, M.A.E., D. Korzec and M. Ismail, 2009. High throughput architecture for OCTAGON network on chip. Proceedings of the 16th IEEE International Conference on Electronics, Circuits and Systems, December 13-16, 2009, IEEE, New York, USA., ISBN: 978-1-4244-5090-9, pp. 101-104.

- Muralimanohar, N., R. Balasubramonian and N. Jouppi, 2007. Optimizing NUCA organizations and wiring alternatives for large caches with CACTI 6.0. Proceedings of the 40th Annual IEEE/ACM International Symposium on Microarchitecture, December 1-5, 2007, IEEE Computer Society, New York, USA., ISBN: 0-7695-3047-8, pp. 3-14.

- Neeb, C. and N. Wehn, 2008. Designing efficient irregular networks for heterogeneous systems-on-chip. J. Syst. Archit., 54: 384-396.

- Ogras, U.Y., J. Hu and R. Marculescu, 2005. Key research problems in NoC design: A holistic perspective. Proceedings of the 3rd IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis, September 19-21, 2005, ACM, New York, USA., ISBN:1-59593-161-9, pp: 69-74.

- Pande, P.P., C. Grecu, A. Ivanov and R. Saleh, 2003. High-throughput switch-based interconnect for future SoCs. Proceedings of the 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications, July 2-2, 2003, IEEE, Vancouver, British Columbia, Canada, ISBN: 0-7695-1944-X, pp. 304-310.

- Paukovits, C. and H. Kopetz, 2008. Concepts of switching in the time-triggered network-on-chip. Proceedings of the 2008 14th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, August 25-27, 2008, IEEE, Vienna, Austria, ISBN: 978-0-7695-3349-0, pp: 120-129.

- Pena, R.J.C. and P.R. Michel, 2011. Network on chip architectures for high performance digital signal processing using a configurable core. Proceedings of the 2011 International Conference on Reconfigurable Computing and FPGAs, November 30-December 2, 2011, IEEE, Guadalajara, Mexico, ISBN: 978-1-4577-1734-5, pp: 375-379.

- Penolazzi, S. and A. Jantsch, 2006. A high level power model for the Nostrum NoC. Proceedings of the 9th EUROMICRO Conference on Digital System Design (DSD'06), August 30-September 1, 2006, IEEE, New York, USA., ISBN: 0-7695-2609-8, pp. 673-676.

- Postman, J., T. Krishna, C. Edmonds, L.S. Peh and P. Chiang, 2013. Swift: A low-power network-on-chip implementing the token flow control router architecture with swing-reduced interconnects. IEEE. Trans. Very Large Scale Integr. Syst., 21: 1432-1446.

- Qouneh, A., Z. Li, M. Joshi, W. Zhang and X. Fu et al., 2012. Aurora: A thermally resilient photonic network-on-chip architecture. Proceedings of the IEEE 30th International Conference on Computer Design (ICCD), September 30-October 3, 2012, IEEE, New York, USA., ISBN: 978-1-4673-3052-7, pp: 379-386.

- Radulescu, A. and K. Goossens, 2004. Communication services for networks on chip. Domain Specific Processors Syst. Archit. Model. Simul., 2004: 193-213.

- Rijpkema, E., K. Goossens, A. Radulescu, J. Dielissen and J.V. Meerbergen et al., 2003. Trade-offs in the design of a router with both guaranteed and best-effort services for networks on chip. IEEE. Proc. Comput. Digital Tech., 150: 294-302.

- Rufas, D.C., J. Joven and J. Carrabina, 2006. A validation and performance evaluation tool for ProtoNoC. Proceedings of the 2006 International Symposium on System-on-Chip, November 13-16, 2006, IEEE, New York, USA., ISBN: 1-4244-0621-8, pp. 1-4.

- Salminen, E., T. Kangas, T.D. Hamalainen, J. Riihimaki and V. Lahtinen *et al.*, 2006. HIBI communication network for system-on-chip. J. VLSI. Signal Process. Syst. Signal Image Video Technol., 43: 185-201.

- Samuelsson, H., and S. Kumar, 2004. Ring road NoC architecture. Proceedings of the Conference on Norchip, November 8-9, 2004, IEEE, New York, USA., ISBN: 0-7803-8510-1, pp: 16-19.

- Schoeberl, M., 2007. A time-triggered network-on-chip. Proceedings of the 2007 International Conference on Field Programmable Logic and Applications, August 27-29, 2007, IEEE, New York, USA., ISBN: 978-1-4244-1059-0, pp. 377-382.

- Schuck, C., S. Lamparth and J. Becker, 2007. Artnoc-A novel multi-functional router architecture for Organic Computing. Proceeding of the 2007 International Conference on Field Programmable Logic and Applications, August 27-29, 2007, IEEE, New York, USA., ISBN: 978-1-4244-1059-0, pp: 371-376.

- Seifi, M.R. and M. Eshghi, 2012. Clustered NOC, a suitable design for group communications in network on Chip. Comput. Electr. Eng., 38: 82-95.

- Sethi, M.A.J., F.A. Hussin and N.H. Hamid, 2013a. Implementation of biological sprouting algorithm for NoC fault tolerance. Proceedings of the 2013 IEEE International Conference on Circuits and Systems (ICCAS), September 18-19, 2013, IEEE, New York, USA., ISBN: 978-1-4799-1337-4, pp: 39-44.

- Sethi, M.A.J., F.A. Hussin and N.H. Hamid, 2013b. Synaptogenesis based bio-inspired NoC fault tolerant interconnects. Proceedings of the IEEE International Conference on Control System, Computing and Engineering (ICCSCE), November 29-December 1, 2013, IEEE, New York, USA., ISBN: 978-1-4799-1508-8, pp. 46-51.

- Sethi, M.A.J., F.A. Hussin and N.H. Hamid, 2014. Bio-inspired NoC fault tolerant techniques. Proceedings of the 2014 5th International Conference on Intelligent and Advanced Systems (ICIAS), June 3-5, 2014, IEEE, New York, USA., ISBN: 978-1-4799-4653-2, pp. 1-6.

- Sethi, M.A.J., F.A. Hussin and N.H. Hamid, 2016a. Bio-inspired NoC fault tolerant techniques using guaranteed throughput and best effort services. Integr. VLSI. J., 54: 65-96.

- Sethi, M.A.J., F.A. Hussin and N.H. Hamid, 2016b. Implementation and analysis of biological synaptogenesis technique on nodes and interconnects for NoC fault tolerance. Res. J. Appl. Sci., Eng. Technol., 12: 483-489.

- Shanthi, M.D.A.D., 2014. FPGA based adaptive resource efficient error control methodology for network on chip. Res. J. Appl. Sci., 9: 48-52.

- Soteriou, V., N. Eisley, H. Wang, B. Li and L.S. Peh, 2007.

Polaris: A system-level roadmap for on-chip interconnection networks. Proceedings of the 2006 International Conference on Computer Design, October 1-4, 2006, IEEE, New York, USA., ISBN: 978-0-7803-9706-4, pp. 134-141.

- Stefan, R.A., A. Molnos and K. Goossens, 2014. Daelite: A tdm noc supporting qos, multicast and fast connection set-up. IEEE. Trans. Comput., 63: 583-594.

- Stensgaard, M.B. and J. Sparso, 2008. Renoc: A network-on-chip architecture with reconfigurable topology. Proceedings of the 2nd ACM/IEEE International Symposium on Networks-on-Chip, April 7-10, 2008, IEEE, New York, USA., ISBN: 978-0-7695-3098-7, pp: 55-64.

- Taylor, M.B., J. Kim, J. Miller, D. Wentzlaff and F. Ghodrat et al., 2002. The raw microprocessor: A computational fabric for software circuits and general-purpose programs. IEEE Micro, 22: 25-35.

- Teehan, P., M. Greenstreet and G. Lemieux, 2007. A survey and taxonomy of GALS design styles. IEEE. Design Test Comput., 24: 418-428.

- Tortosa, D.S., T. Ahonen and J. Nurmi, 2004. Issues in the development of a practical NoC: The proteo concept. Integr. VLSI. J., 38: 95-105.

- Vangal, S.R., J. Howard, G. Ruhl, S. Dighe and H. Wilson *et al.*, 2008. An 80-tile sub-100-w teraflops processor in 65-nm cmos. Solid State Circuits IEEE. J., 43: 29-41.

- Wang, C., W.H. Hu, S.E. Lee and N. Bagherzadeh, 2011. Area and power-efficient innovative congestionaware network-on-chip architecture. J. Syst. Archit., 57: 24-38.

- Wang, N., A. Sanusi, P.Y. Zhao, M. Elgamel and M.A. Bayoumi, 2010. PMCNOC: A pipelining multi-channel central caching network-on-chip communication architecture design. J. Signal Process. Syst., 60: 315-331.

- Wang, X., T. Ahonen and J. Nurmi, 2007. Applying CDMA technique to network-on-chip. IEEE. Trans. Very Large Scale Integr. Syst., 15: 1091-1100.

- Wiklund, D. and D. Liu, 2003. SoCBUS: Switched network on chip for hard real time embedded systems. Proceedings of the International Conference on Parallel and Distributed Processing, April 22-26, 2003, IEEE, New York, USA., ISBN: 0-7695-1926-1, pp. 1-8.

- Wingard, D., 2001. MicroNetwork-based integration for SOCs. Proceedings of the Conference on Design Automation, June 22-22, 2001, IEEE, New York, USA., ISBN: 1-58113-297-2, pp. 673-677.

- Wolkotte, P.T., G.J. Smit, G.K. Rauwerda and L.T. Smit, 2005. An energy-efficient reconfigurable circuitswitched network-on-chip. Proceedings of the 19th IEEE International Symposium on Parallel and Distributed Processing, April 4-8, 2005, IEEE, New York, USA., ISBN: 0-7695-2312-9, pp: 155-155.

- Wu, L.W., W.X. Tang and Y. Hsu, 2011. A novel architecture and routing algorithm for dynamic reconfigurable network-on-chip. Proceedings of the 2011 IEEE 9th International Symposium on Parallel and Distributed Processing with Applications, May 26-28, 2011, IEEE, New York, USA., ISBN: 978-1-4577-0391-1, pp: 177-182.

- Yaghini, P.M., A. Eghbal and N. Bagherzadeh, 2015. On the design of hybrid routing mechanism for meshbased network-on-chip. Integr. VLSI J., 50: 183-192.

- Yang, Y.S., R. Kumar, G. Choi and P.V. Gratz, 2014. WaveSync: Low-latency source-synchronous bypass network-on-chip architecture. ACM. Trans. Des. Autom. Electron. Syst., 19: 34-34.

- Zeferino, C.A. and A.A. Susin, 2003. SoCIN: A parametric and scalable network-on-chip. Proceedings of the 16th Symposium on Integrated Circuits and Systems Design, September 8-11, 2003, IEEE, New York, USA., ISBN: 0-7695-2009-X, pp: 169-174.

- Zeferino, C.A., M.E. Kreutz and A.A. Susin, 2004. RASoC: A router soft-core for networks-on-chip. Proceedings of the IEEE Conference on Design, Automation and Test in Europe and Exhibition, Feburary 16-20, 2004, IEEE, New York, USA., ISBN: 0-7695-2085-5, pp: 198-203.